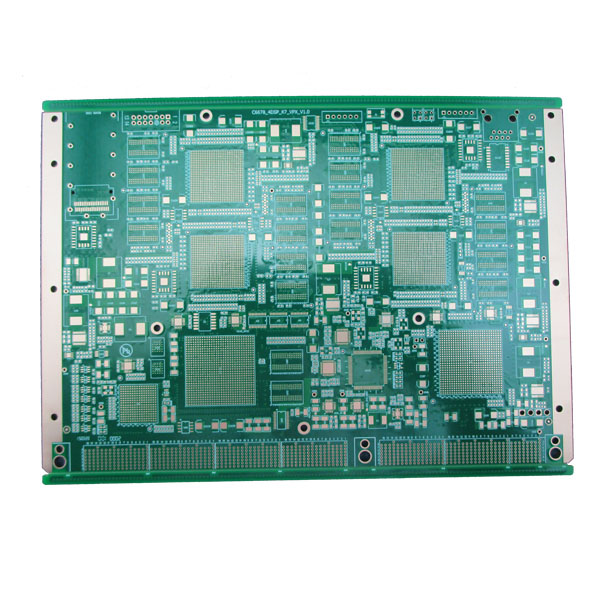

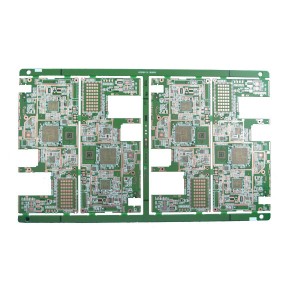

22 lớp HDI PCB cho quân sự và quốc phòng

Thông tin chi tiết sản phẩm

| Lớp | 22 lớp |

| Độ dày bảng | 3.0MM |

| Vật chất | Rogers 4350B |

| Độ dày đồng | 1 OZ (35um) |

| Kết thúc bề mặt | (ENIG) Vàng ngâm |

| Lỗ nhỏ nhất (mm) | 0,25mm |

| Qua công nghệ | Qua cắm bằng nhựa thông |

| Chiều rộng dòng tối thiểu (mm) | 0,10mm (4 triệu) |

| Khoảng cách dòng tối thiểu (mm) | 0,10mm (4 triệu) |

| Mặt nạ Hàn | màu xanh lá |

| Màu huyền thoại | trắng |

| Trở kháng | Trở kháng đơn & Trở kháng vi sai |

| Đóng gói | Túi chống tĩnh điện |

| Kiểm tra điện tử | Bay thăm dò hoặc vật cố định |

| Tiêu chuẩn chấp nhận | IPC-A-600H Lớp 2 |

| Ứng dụng | Quân sự và quốc phòng |

1. Giới thiệu

HDI là viết tắt của High Density Interconnector. Một bảng mạch có mật độ dây cao hơn trên một đơn vị diện tích so với bảng thông thường được gọi là HDI PCB. HDI PCB có không gian và đường nét tốt hơn, vias nhỏ và miếng đệm chụp và mật độ đệm kết nối cao hơn. Nó rất hữu ích trong việc nâng cao hiệu suất điện và giảm trọng lượng và kích thước của thiết bị. HDI PCB là lựa chọn tốt hơn cho số lượng lớp cao và bảng nhiều lớp đắt tiền.

Các lợi ích chính của HDI

Khi nhu cầu của người tiêu dùng thay đổi, công nghệ cũng phải thay đổi. Bằng cách sử dụng công nghệ HDI, các nhà thiết kế hiện có tùy chọn để đặt nhiều thành phần hơn ở cả hai mặt của PCB thô. Nhiều quá trình thông qua, bao gồm thông qua trong pad và mù thông qua công nghệ, cho phép các nhà thiết kế nhiều bất động sản PCB hơn để đặt các thành phần nhỏ hơn thậm chí gần nhau hơn. Kích thước và cao độ thành phần giảm xuống cho phép nhiều I / O hơn ở các hình học nhỏ hơn. Điều này có nghĩa là truyền tín hiệu nhanh hơn và giảm đáng kể suy hao tín hiệu và độ trễ qua đường.

Các công nghệ trong HDI PCB

- Blind Via: Sự tiếp xúc của một lớp bên ngoài kết thúc với một lớp bên trong

- Chôn qua: Lỗ xuyên qua các lớp lõi

- Microvia: Blind Via (coll. Cũng qua) với đường kính ≤ 0,15mm

- SBU (Sequential Build-Up): Tích tụ lớp tuần tự với ít nhất hai thao tác nhấn trên PCB nhiều lớp

- SSBU (Xây dựng bán tuần tự): Ép các cấu trúc con có thể kiểm tra được trong công nghệ SBU

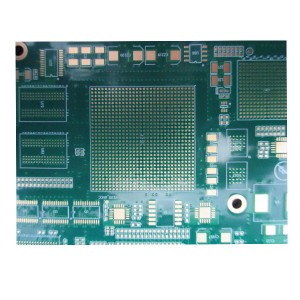

Via in Pad

Cảm hứng từ công nghệ gắn kết bề mặt từ cuối những năm 1980 đã đẩy giới hạn của BGA, COB và CSP thành bề mặt vuông nhỏ hơn inch. Quá trình via in pad cho phép đặt vias bên trong bề mặt của các vùng đất bằng phẳng. Các lỗ thông được mạ và đổ đầy epoxy dẫn điện hoặc không dẫn điện, sau đó đậy nắp và mạ lên, làm cho nó hầu như không nhìn thấy.

Nghe có vẻ đơn giản nhưng có trung bình tám bước bổ sung để hoàn thành quy trình độc đáo này. Thiết bị chuyên dụng và kỹ thuật viên được đào tạo theo quy trình chặt chẽ để đạt được độ ẩn hoàn hảo.

Qua các loại điền

Có nhiều loại vật liệu trám trét khác nhau: epoxy không dẫn điện, epoxy dẫn điện, đồng đầy, bạc lấp đầy và mạ điện hóa. Tất cả những điều này dẫn đến việc chôn vùi trong một vùng đất bằng phẳng sẽ hoàn toàn được hàn lại như những vùng đất bình thường. Vias và microvias được khoan, làm mù hoặc chôn lấp, lấp đầy sau đó được mạ và ẩn bên dưới vùng đất SMT. Xử lý vias kiểu này đòi hỏi thiết bị đặc biệt và tốn nhiều thời gian. Nhiều chu kỳ khoan và khoan sâu được kiểm soát làm tăng thêm thời gian xử lý.

Công nghệ máy khoan Laser

Việc khoan những vias nhỏ nhất cho phép tạo ra nhiều công nghệ hơn trên bề mặt bảng. Sử dụng chùm ánh sáng có đường kính 20 microns (1 Mil), chùm ánh sáng có ảnh hưởng cao này có thể cắt xuyên qua kim loại và thủy tinh tạo ra các lỗ cực nhỏ. Các sản phẩm mới tồn tại như vật liệu thủy tinh đồng nhất là một tấm laminate có tổn thất thấp và hằng số điện môi thấp. Những vật liệu này có khả năng chịu nhiệt cao hơn để lắp ráp không có chì và cho phép sử dụng các lỗ nhỏ hơn.

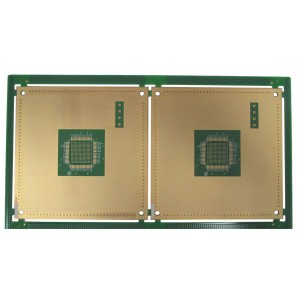

Cán & Vật liệu cho Ban HDI

Công nghệ đa lớp tiên tiến cho phép các nhà thiết kế thêm tuần tự các cặp lớp bổ sung để tạo thành PCB đa lớp. Việc sử dụng máy khoan laser để tạo lỗ ở các lớp bên trong cho phép mạ, tạo hình và khắc trước khi ép. Quá trình thêm vào này được gọi là xây dựng tuần tự. Chế tạo SBU sử dụng vias được làm đầy rắn cho phép quản lý nhiệt tốt hơn, kết nối liên kết mạnh hơn và tăng độ tin cậy của bo mạch.

Đồng phủ nhựa được phát triển đặc biệt để hỗ trợ chất lượng lỗ kém, thời gian khoan lâu hơn và cho phép PCB mỏng hơn. RCC có cấu hình cực thấp và lá đồng siêu mỏng được gắn với các nốt sần nhỏ trên bề mặt. Vật liệu này được xử lý hóa học và sơn lót cho công nghệ tạo đường và khoảng cách mỏng nhất, tốt nhất.

Việc áp dụng điện trở khô cho tấm laminate vẫn sử dụng phương pháp cuộn nóng để áp dụng điện trở cho vật liệu cốt lõi. Quy trình công nghệ cũ hơn này, hiện tại người ta khuyên nên làm nóng vật liệu đến nhiệt độ mong muốn trước khi tiến hành cán màng cho bảng mạch in HDI. Việc làm nóng sơ bộ vật liệu cho phép áp dụng ổn định chất chống khô lên bề mặt của tấm ép tốt hơn, kéo ít nhiệt ra khỏi các cuộn nóng và cho phép nhiệt độ thoát ra ổn định nhất quán của sản phẩm nhiều lớp. Nhiệt độ lối vào và lối ra phù hợp dẫn đến ít không khí bám bên dưới màng hơn; điều này rất quan trọng đối với việc tái tạo các đường nhăn và khoảng cách.